電賽匯總(四) 電路電源模塊設(shè)計(jì)與集成電路設(shè)計(jì)

在電子設(shè)計(jì)競(jìng)賽中,電路電源模塊設(shè)計(jì)與集成電路設(shè)計(jì)是決定系統(tǒng)性能與穩(wěn)定性的關(guān)鍵環(huán)節(jié)。電源模塊負(fù)責(zé)為整個(gè)系統(tǒng)提供穩(wěn)定、高效的能源,而集成電路設(shè)計(jì)則直接影響系統(tǒng)的集成度與功能實(shí)現(xiàn)。本文將圍繞這兩大主題展開(kāi),介紹其設(shè)計(jì)要點(diǎn)與常見(jiàn)方案。

一、電路電源模塊設(shè)計(jì)

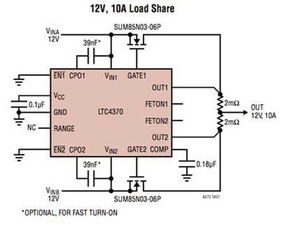

電源模塊是電子系統(tǒng)的“心臟”,其設(shè)計(jì)需綜合考慮效率、穩(wěn)定性、噪聲抑制等因素。常見(jiàn)設(shè)計(jì)包括線性電源與開(kāi)關(guān)電源兩類:

1. 線性電源:結(jié)構(gòu)簡(jiǎn)單、噪聲低,適用于對(duì)噪聲敏感的小功率場(chǎng)合,但效率較低。

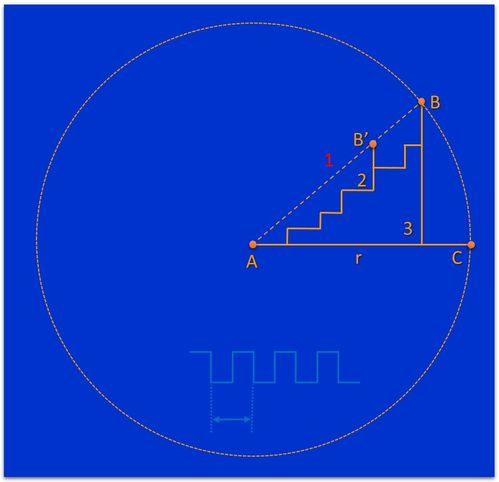

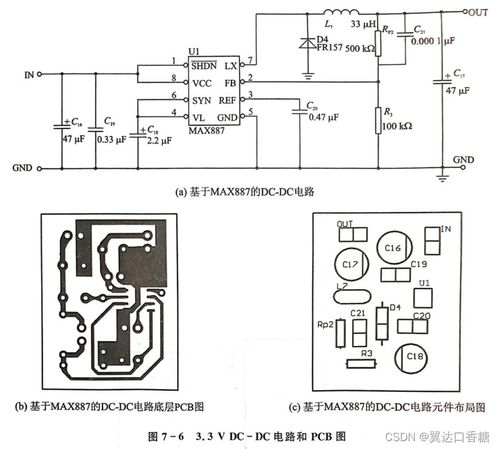

2. 開(kāi)關(guān)電源:效率高、體積小,適合大功率應(yīng)用,但設(shè)計(jì)需注意電磁干擾問(wèn)題。

設(shè)計(jì)時(shí)需根據(jù)系統(tǒng)需求選擇合適的拓?fù)浣Y(jié)構(gòu)(如Buck、Boost、LDO等),并注重濾波與保護(hù)電路的設(shè)計(jì),確保輸出電壓紋波小、負(fù)載調(diào)整率高。

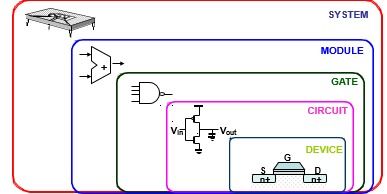

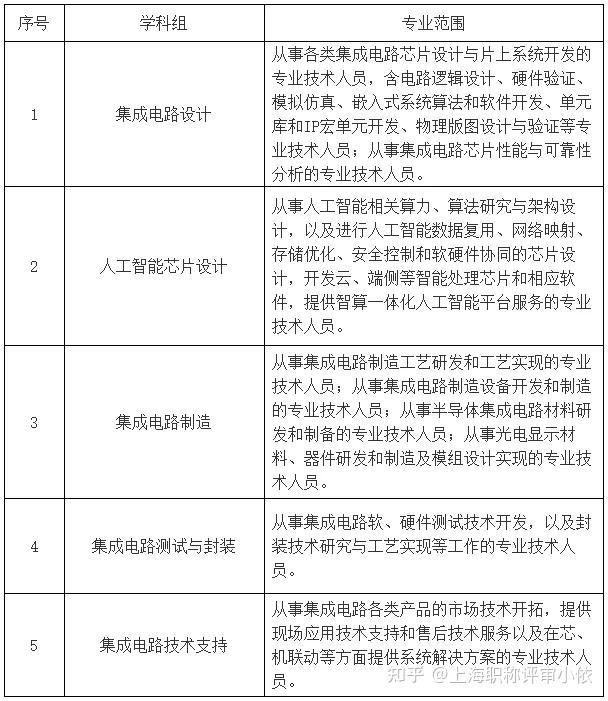

二、集成電路設(shè)計(jì)

集成電路設(shè)計(jì)旨在將多個(gè)功能模塊集成到單一芯片上,以提升系統(tǒng)性能并減小體積。設(shè)計(jì)過(guò)程包括:

1. 架構(gòu)設(shè)計(jì):根據(jù)系統(tǒng)功能定義芯片的整體結(jié)構(gòu)。

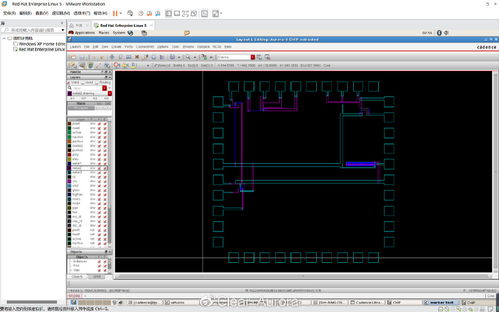

2. 電路設(shè)計(jì):使用EDA工具進(jìn)行晶體管級(jí)設(shè)計(jì),優(yōu)化功耗、速度等參數(shù)。

3. 版圖設(shè)計(jì):將電路轉(zhuǎn)換為物理布局,需考慮寄生效應(yīng)與工藝限制。

4. 驗(yàn)證與測(cè)試:通過(guò)仿真與實(shí)測(cè)確保芯片功能正確。

在電賽中,常采用FPGA或現(xiàn)成IC進(jìn)行快速原型開(kāi)發(fā),但掌握IC設(shè)計(jì)基礎(chǔ)有助于優(yōu)化系統(tǒng)性能。

三、設(shè)計(jì)實(shí)例與注意事項(xiàng)

以電賽常見(jiàn)題目為例,如設(shè)計(jì)一個(gè)多路輸出電源模塊:

- 可采用開(kāi)關(guān)電源為主輸出,LDO為噪聲敏感模塊供電。

- 集成電路部分可集成電壓監(jiān)控、保護(hù)邏輯等功能。

注意事項(xiàng):

- 電源模塊需預(yù)留余量,避免滿載時(shí)電壓跌落。

- IC設(shè)計(jì)需注意散熱與信號(hào)完整性,高頻場(chǎng)景下應(yīng)優(yōu)化布線。

電源模塊與集成電路設(shè)計(jì)相輔相成,在電賽中需結(jié)合實(shí)際需求選擇合適方案,注重穩(wěn)定性與效率的平衡,并通過(guò)仿真與測(cè)試不斷優(yōu)化設(shè)計(jì)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.gxli.com.cn/product/42.html

更新時(shí)間:2026-01-10 13:09:35